Within this article the author John ( G8GKU ) indicates how two typical AD9850 modules may be utilized and controlled so as to produce the often needed pair of R.F. carriers with a quadrature phase relationship, sine or cos (0° or 90°). These modules are readily available from online suppliers.

A pair of quadrature related sine waves are useful if not mandatory when making SSB modulators / demodulators, image reject mixers, Weaver method SSB ( Tx / Rx ) and similar items.

An accompanying demonstration code has been written to allow a user to set output frequency and phase of the two DDS units.

The popular Arduino™ platform has been chosen as controller for the DDS synthesisers, C++ Arduino code being written by Alex. However, to broaden the appeal, a version has also been coded which will run on a PIC™ 16F876 28 pin DIP device, written by G8GKU, providing home-brew readers an opportunity to warm up the soldering iron and build a system from scratch.

Download of the necessary hex file for the PIC 16F876 is available :

Hex_Files

… and the Arduino equivalent is available here:

dds

Source of information regarding the Analogue Devices™ AD9850 devices is to be found at http://www.analog.com/media/en/technical-documentation/data-sheets/AD9850.pdf

A very specific and relevant application note by Analogue Devices is to be found at http://www.analog.com/media/en/technical-documentation/application-notes/AN-587.pdf

The author wishes to acknowledge, with thanks, the detailed technical information contained within the two publications by Analog Devices.

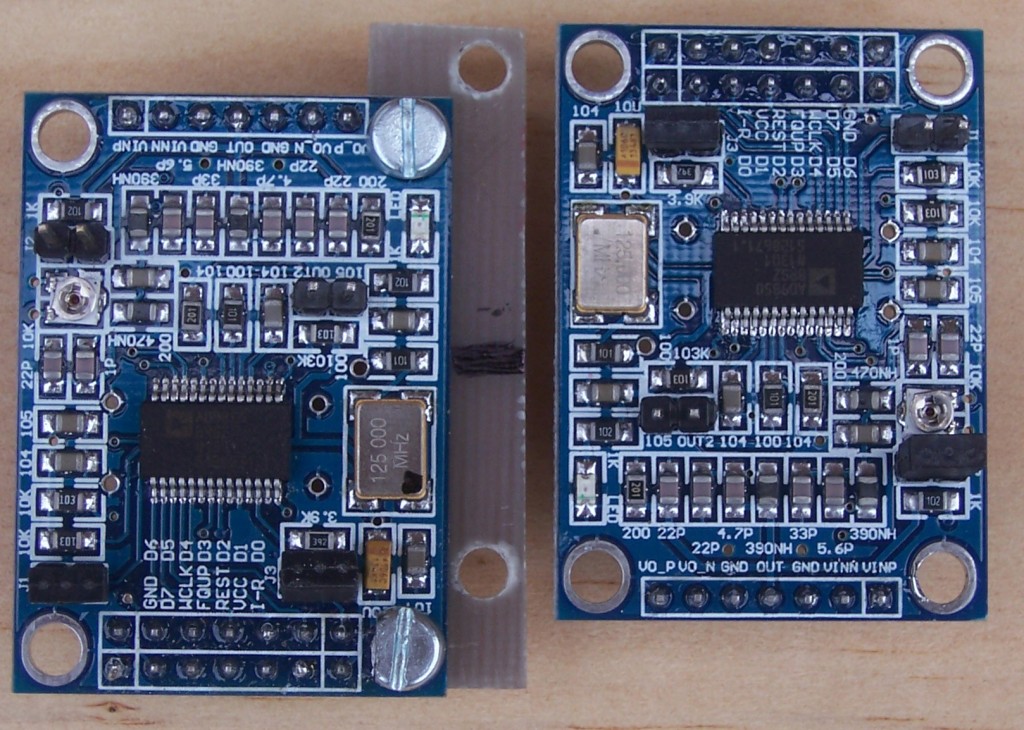

Photograph 1 shows the pair of DDS modules used by the author, however, there are other schematically similar but physically different PCBs to be obtained, the on-board circuitry is very similar and readers may well use their own choice of DDS module.

Photograph 1:

Overall the process consists of two parts:

Part one details the hardware implementation.

Part two introduces the procedure required to drive the physical DDS cores to produce the quadrature output waveforms.

Hardware Implementation

One small change is required to just one of the two DDS PCBs. The two DDS units are then physically mounted such that the DDS modules are close together, in a position which will allow the high speed crystal clock signal from one unit to be jumper-wired across to the second unit.

To allow the generation of frequency and phase locked quadrature outputs it is essential that both DDS modules share just one clock oscillator.

Note, Photograph 1 shows the M3 mounting screw-head adjacent to the double row of PCB connector pins, with the inside edge of the screw head filed back 1 mm. This is suggested as the DDS PCB has a signal track rather close to the hole. It is under the white indent paint and can easily be overlooked. Do this, at one position, for both DDS PCBs.

Photograph 1 indicates how the two DDS modules should be mounted, side by side and long-ways reversed, with ca 5.5 mm lengthways offset between them. This mounting method will allow the 125 MHz clock from one module to be passed across to the second module via a short wire, so keeping the two DDS clock signals closely in step as per the AN-587.pdf application note. Also visible is the strongly suggested addition of a short length of single sided PCB material, resulting in an overall mechanically firm assembly.

Required physical modification of DDS PCB.

It is required to modify just one of the DDS PCB modules, plus an extra option as mentioned below. In overview, one resistor is to lifted up on end and then a wire link added using as short a length of wire as is possible. Please view the wiring schematic sheet at this stage.

Method

Re photograph 1, the resistor to be lifted is indicated by the adjacent ink mark line on the joining PCB. This is a 100 Ohm resistor fitted between the xtal clock oscillator signal output ( pin 3 ) and the clock input to the AD9850 chip itself. The resistor and local circuitry is shown in very simplified fashion within the wiring diagram.

Choose one module on which the resistor is to be lifted to the vertical, on this DDS PCB the clock oscillator is then unused.

Using a small soldering iron, heat the soldered resistor pads by swapping end to end and lift it off the PCB with small tweezers, putting it in a safe place! Note, apply enough heat to not only melt the solder but also perhaps to melt the mounting glue used to affix the resistor before it was originally soldered.

Once the resistor is removed, ensure the then exposed PCB pads are free of solder spikes, perhaps applying a little new solder to the one vacated solder pad which is the inside-most pad, i.e. far-most from the PCB edge.

Refit the resistor so as to be vertical, on the inside pad, soldering one end to the pad. This so-called ‘ Tombstone ‘ fitting of the resistor is not strong and appropriate care is now needed when handling the PCB.

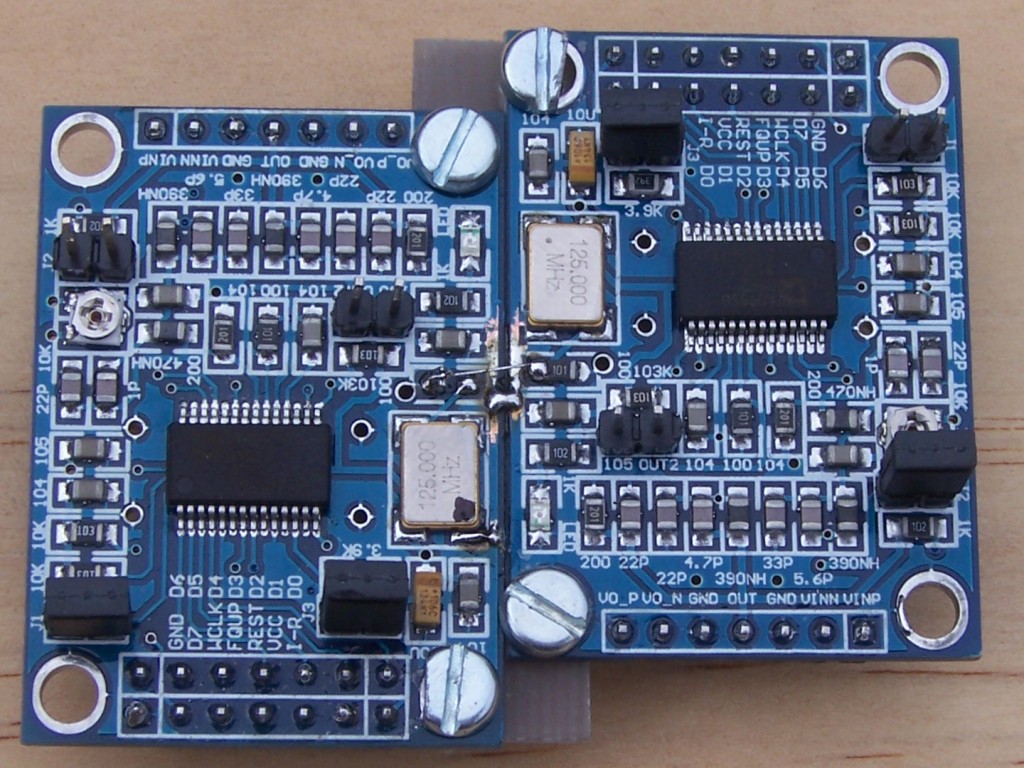

Consider the optional modification as below and then proceed to assemble the two PCBs side by as in photograph 2.

Photograph 2:

An Optional Modification

Optionally, the now unused clock oscillator module upon the DDS PCB which has been modified may be disabled, i.e. turned off. This has the advantage of saving the 40 mA or so of oscillator power supply demand and also removing the presence of an un-needed 125 MHz carrier which may be detected by nearby suitable Rx’s. To disable the oscillator module, proceed as follows :

Locate the oscillator module, it is the 7 x 5 mm metal clad component near the board edge.

Next locate pin 1 of the crystal module, it is the pin which is closest to both the board edge and the nearest PCB mounting hole. It is adjacent to the ‘ dot ‘ on the oscillator top cover. Clean off the paint from a 2 mm section of the PCB ground track just adjacent to pin 1 of the oscillator, there is a thin continuous ground track which runs past the module. Solder a 1.5 mm link, using thin wire, between the pin 1 pad of the oscillator and the cleaned PCB ground track. Job done.

Assembling the Two DDS Units

This section addresses assembling the two DDS units to be one module.

To provide workable physical strength a short strip of single sided copper clad PCB material is used to join two DDS PCBs, this may be glass fibre ( fiber ) PCB or other material. Suggested size of the material is 46 mm long by 11 mm wide. Two holes along each long edge are required, which are easiest to mark with a felt tip pen through the fixing holes of the DDS modules.

Mark holes on to the glass side and not the copper side of the strip. Photograph 1 shows the general technique.

Repeated from above ;

Please note, viewing Photograph 1 shows the M3 screw-head adjacent to the double row of PCB connector pins to have the inside edge of the screw head filled back 1 mm, this is needed as the DDS PCB has a signal track rather too close to the hole. It is under the indent paint and can easily be overlooked. Do this for both DDS PCBs.

The assembly is completed by bonding the pair of DDS PCBs together with the PCB joining material by use of either M3 or other slim nuts and bolts. Ensure that the joining plate has the copper side *away* from the DDS PCBs when assembling, take care not to allow a screwdriver to slip during this process, as it may damage surface mount components of the DDS modules.

These 4 non-insulated screws provide, via the PCB material, an additional overall ground connection between the two DDS modules. To allow the combined dual DDS assembly to stand on the bench for testing the author has fitted longer M3 screws to the four outside fixing holes to act as legs, nothing more.

Before fitting the clock signal wire link, carefully clean off the ground-track paint from a 3 mm length of the track, at both PCB edges just between the two 100 Ohm resistors. Once clean add a small ( about 2 mm ) bridging solder blob so as to join the ground tracks. This can be seen on photograph 2 ( it may be easier to remove the paint before final physical assembly ).

The wire link for the clock signal is next to be fitted. It should be taken from the non-modified DDS PCB, from the *outside* pad of the corresponding resistor which was lifted on the other PCB. The destination of the wire link is the top, i.e. free end, of the uplifted 100 Ohm resistor.

Use of thin enameled wire will reduce risk of unwanted connections, the wire link is about 7 mm long.

Physical Wiring

The diagram above shows the detailed pin to pin data signal wiring between the controller and the DDS module. However, please read the following application note.

Application note AN587 places strong emphasis upon the need for both the master clock to the DDS modules and the Frequency Update ( Fr_updt ) pulse to be applied with the same time, phase, relationship to each DDS in the system.

In particular the Fr_updt pulse should be a fast rising edge and should have the same physical wire length between the CPU / controller pin and to each DDS unit. It is *not correct* to daisy chain the Fr_updt pulse from the controller to a first DDS and then to pass it along to the second unit. The correct method is to fork, i.e. to split, the wire a little way before the wire reaches either one of the DDS units and to take one each of the forked wires to a DDS Fr_updt pin, keeping the wire lengths after the fork to closely the same length. This method will provide a Fr_updt pulse well time-matched to each DDS core. Likewise, the link-jumpered master clock signal will also be as close to in-phase as can be practically done by the close physical assembly of the two DDS units.

Part two introduces the code and operating procedure required to drive the physical units.

There is little in the code which will not be found in just about any code which drives an AD9850 module. What makes the code for this article different is that it sequences the start up of the two DDS cores in the correct fashion so as to run not only at the same frequency but with a quadrature phase relationship.

The DDS start-up sequence in this article refers to the DDS units as operated in the serial mode of data loading, the parallel mode is only slightly different.

Overall the process consists of clearing all of the registers of the two DDS units and then starting both, at the required frequency and phase angle with a single “ go “ pulse from the controller. However, the AD9850 has some subtle characteristics which are important to the start up process.

Although contained within the data sheet, what is quite easily overlooked is the information that the AD9850 device always starts-up in parallel data entry mode at any reset pulse application.

Added to this situation is that the very first ‘ data-load clock pulse, Fr_updt pulse pair ‘ ( in that order ) following a reset always has the task of loading the internal 8 bit control and phase register of the AD9850, keep in mind this is an 8 bit parallel load event. In this application, it is required that the AD9850 starts at “ zero phase “ or some other selectable phase. Therefore the relevant bits of the phase control word must be pre-set, at the very first ‘data-load clock pulse Fr_updt pulse pair’. The solution used in this article is to ensure the phase control bits are held, wired, at logic 0 during the first data-load clock pulse, Fr_updt pulse pair. It is then the responsibility of the second update pulse to load the actual required phase and frequency data. To ensure the initial phase select bits are at logic zero, in the case of the DDS module used by the author, the data pins, D3, 4, 5, 6 are wire linked to zero volts, i.e. the ground pin of the connector. Data bits 0, 1 are set to logic 1 by on-PCB pull up resistors and a two pin link, J1, grounds data bit 2, giving a byte of 0b00000011, the link is to be fitted. Data bit D7 is the serial data input pin and should be set to logic zero by the CPU and code during the initial stages of the start-up process.

Note, in some of the internet supplied circuit diagrams for the DDS modules used, the schematic has the D7 and GND schematic pins shown in reversed order to the printed indents on the physical PCB. In the case of the PCBs used by the author the indents of the PCB are correct, where GND is the end pin, see photograph 1.

Referring to the AD9850 data sheet, page 24, it will be seen that a pulse applied to the Reset input pin to the AD9850 has the effect of resetting the device to a known zero phase state and with the internal registers also at a known state.

* The reset pulse does not clear or reset the data input shift register. *

Once the reset pulse has passed, the DDS core commences operation and hence the phase accumulator registers will advance in phase at each cycle of the DDS clock. The actual advance in phase and frequency entirely depends upon the initially random bits as will be in the frequency control registers at power up time. So to control both the phase and frequency of the DDS cores once running it is required that the cores are reset, loaded with all zero’s and then reset again, before receiving the user required phase and frequency data. With the above subtlety in mind it can now be understood that a specific start-up sequence is needed to start the two DDS cores in phase and frequency lock step.

To recap, to achieve quadrature operation, it is to essential to reset the device twice and to ensure the correct, i.e. required, phase start-up bits have been set in the control word.

The required detailed sequence is ;

1 Ensure DDS parallel data pins are set as 0,1 high, 2, 3,4,5,6, low.

Above is either hard wired on the PCB or set via appropriate connectors.

Set D7 to logic low, zero, via the CPU and code.

2 Apply first Reset pulse.

Loads phase and control words such that the module will be in “serial“ mode, and phase position = 0°.

3 Serial mode, to each DDS core, shift in 32 all zero bits of frequency bits and 8 bits for phase bits i.e. 0b00000011. Same data to both.

4 Apply one Fr_updt pulse, wired in parallel to both DDS units. Frequency and phase registers now contain “zero frequency and zero Phase”.

5 Apply a second Reset pulse. DDS core does not increment away from all-zero’s as the increment and phase registers are set to all zero’s.

6 Serial mode, shift in 32 bits of required frequency and 0b01000011 for phase bits. To one DDS core only. ( this is the 90 degree offset DDS )

7 Serial mode, shift in 32 bits of required frequency and 0b00000011 for phase bits. To the second DDS core only. ( this is the 0 degree offset DDS )

7 Apply one Fr_updt pulse. The DDS cores now generate the required frequency and will have the as set phase relationship.

In Operation

Once the dual DDS assembly has been completed and connected to the controller of your choice, by whatever is your usual means, load the hex file and run the controller.

It has been assumed that the user will have some form of ASCII serial terminal available on a PC, e.g. HyperTerminal™, TerraTerm or a similar application. Embodied within the code is a simple help menu, which will respond with an on-screen command list. The help menu is invoked by sending the ‘?’ character followed by a new line via the terminal.

The user is given control of each DDS core, each may be set to provide 0 or 90 degrees phase. This allows either DDS core to be either behind or ahead in phase by the required 90 degrees.

Also each DDS module may be set to the same phase, i.e. both at 0 or both at 90 degrees.

Upon initial power-on the controller will set the two cores to be at 1 MHz and at 90 degrees relative to each other.

A testing hint, if you set up to view the two output signals with a dual channel oscilloscope, ensure that the two oscilloscope probes have the same delay / bandwidth factors, if not then expect to see a small and frequency dependent phase shift between the signals.

In most cases where 0, 90 degree signals are used in quadrature mixer drive, it is usual to be able to carefully adjust the amplitude of the signals to be identical. This is relatively easy using the two DDS cores. If one of the two DDS modules is producing a slightly different o/p amplitude this can be corrected. Keeping in mind the note above regarding use of matched oscilloscope probes, determine which of the two DDS core is producing the largest amplitude signal and for that module make the following simple modification. In the case of the DDS modules used by the author, there is a two pin link, labelled J3, this is the ground end of the 3k9 resistor which is used to set the o/p amplitude of the DDS signal, the 3k9 connects to pin 12 of the AD9850.

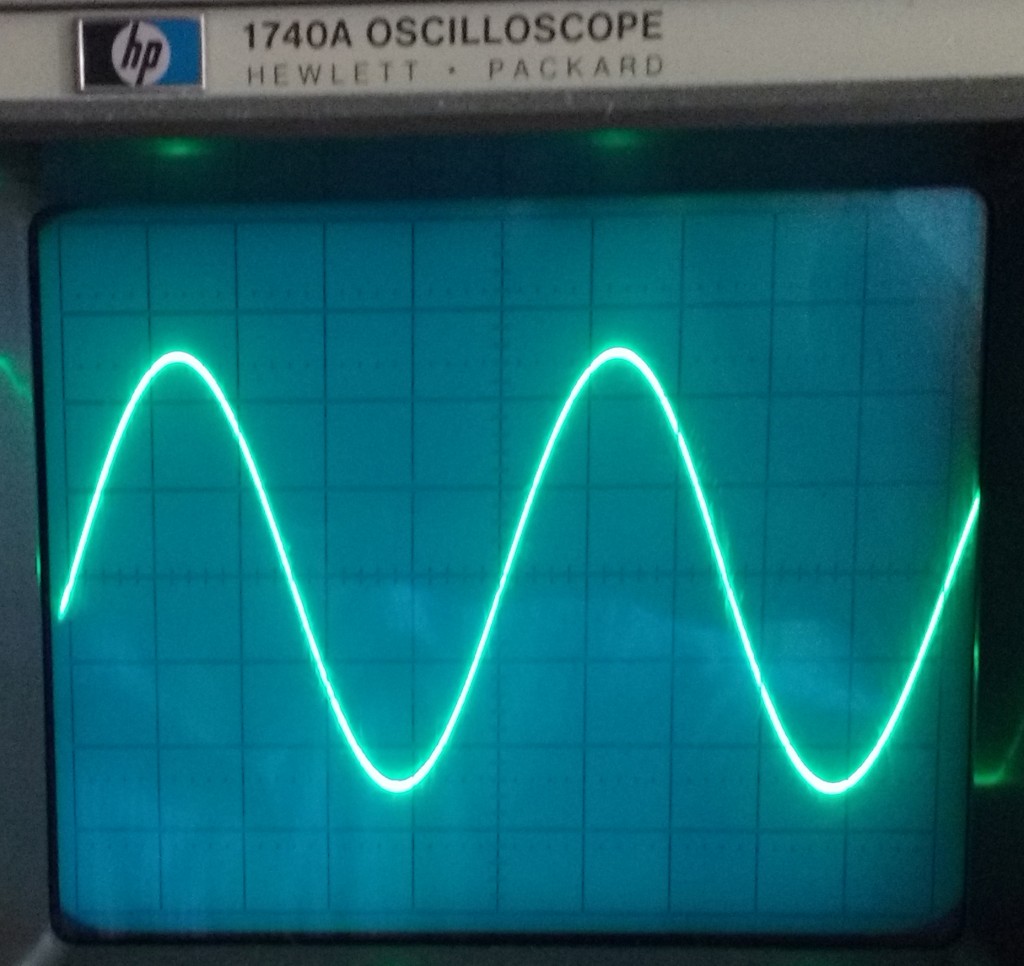

Obtain a physically small 500 Ohm or similar variable resistor. Solder the wiper and one track-end pin across the DDS module PCB-side of the J3 connector and remove the link. Restart the modules and using the 500 Ohm adjust the o/p signal amplitudes to be the same, as shown in photograph 3, which is two 1MHz carriers adjusted to be equal amplitude ( and in phase ).

Photograph 3:

Two signals in quadrature

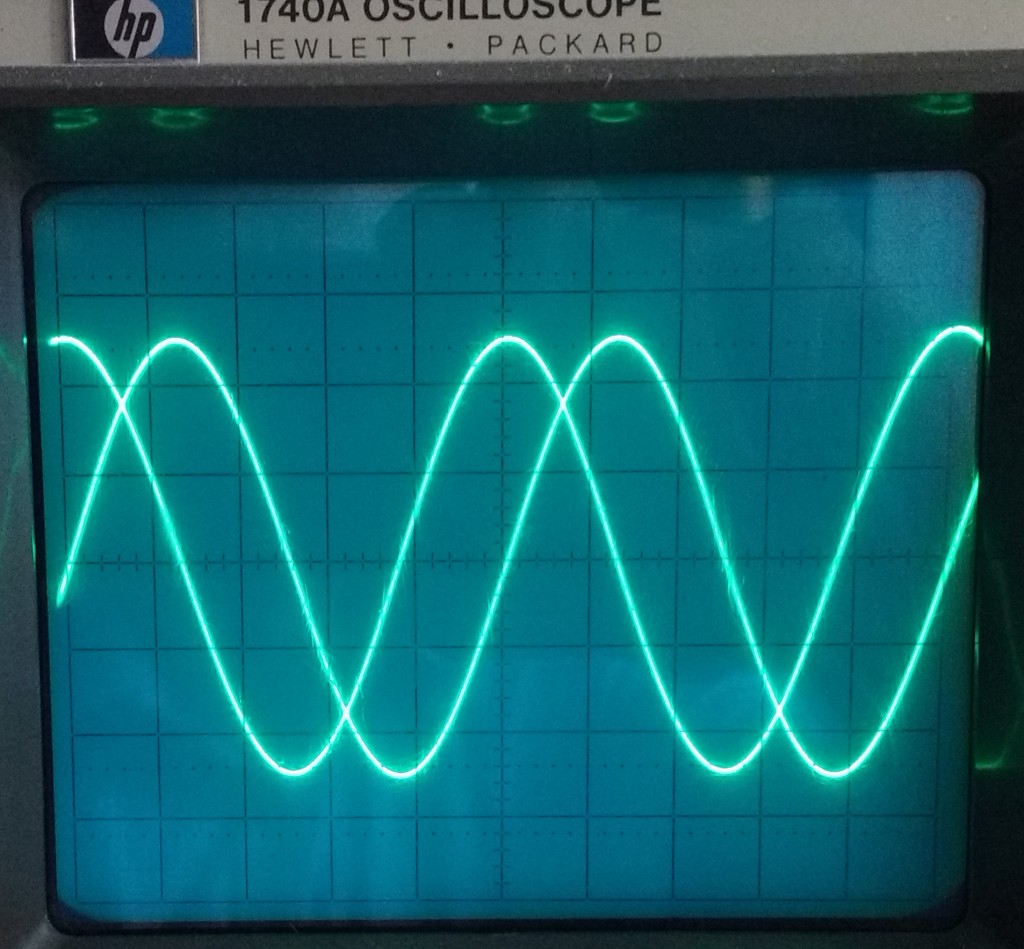

Photograph 4 shows two 1MHz carriers in quadrature.

Photograph 4:

Amplification

As the output signal of the non-amplified DDS core is not sufficient to drive a level 7 mixer, some form of amplification is often used. In the case of quadrature signals it is important that amplification of both signals is identical in amplitude and phase delay.

Notes for 16F876 28 pin version.

The required hardware circuit is essentially the minimum needed to run the device.

In addition to the usual Vcc and ground supplies, plus decoupling capacitors, add as below :

A crystal of 4 or 10MHz at the Osc1 and 2 pins, with 22pF each to ground.

A 100k Ohm pull up resistor on the !MCLR pin to Vcc.

Fit the standard MAX232 style serial interface device to port pins C6 and C7

Load hex code using your usual method.

In both the 4 and 10MHz hex versions the serial port uses 9600,8,none,1,none

i.e. 8 data bits, no parity, 1 stop bit, no flow control.

Connect the DDS units as …

W_CLK_1 PIN_C0 // CHIP PIN 11

W_CLK_2 PIN_C1 // CHIP PIN 12

Serial_Data PIN_C2 // CHIP PIN 13

RESET_DDS PIN_C3 // CHIP PIN 14

Freq_Update PIN_C4 // CHIP PIN 15

Enjoy!

G8GKU 73

Hey, great write up! Just FYI, your Arduino source is 404.

Thank you very much for letting me know, should be fixed now!

I can’t wait to try this. Thanks.

Hello John

I build the arduino nano version … I use a 125 MHz can near both AD9850 modules (they are the old version) and I made some mods in order to watch the frequency in a 16×02 LCD and to enter a new frequency I use a IR remote control …It is working fine …but my Tektronix is a very old osciloscope ..and I dont know if the frequencies up 1MHz still in 90 degrees apart….

In your article you dont write what is the maximum frequency …

Thanks a lot for share this software …

73 from py2ohh miguel

Hello Miguel, Well done indeed on the extensions you have made to the Arduino version of the Dual AD9850 DDS in Quadrature. The maximum frequency expected should be usable, in quadrature, up to the frequency where the reconstruction filters on each of your DDS units start to cut into the response. One small item to consider is that as the working frequency increases, perhaps somewhere past 20 MHz, as the two filters are unlikely to have *exactly* the same precise phase response at the top end of the working range, this may cause a small departure from quadrature in the o/p signals. My test rig here was used to display, on a 100 MHz bandwidth ‘scope, the two quadrature outputs to about 20 MHz, which is where filters of my two instances of the DDS boards begin to take effect. Best wishes, John, G8GKU.

I’d like to see the arduino 16×2 lcd code to display the frequency. I tried but I can’t get the display to clear when I change the frequency. I’m not sure what I’m doing wrong, but if you could post your lcd code that would be great.

I made mine the same as yours but I used a 1/8th watt metal film 100 ohm resistor in place of the smt resistor, and I just soldered a bare wire to each of the crystal oscillator cases to connect the grounds of the dds units.

This is a valuable project. Thanks for posting it!

Hi Alan, thanks for the feedback and apologies for the slow reply! I’ll have a look at the LCD code that I have used for my projects in the past and post that when I’ve got a bit of time if that helps.

When I have used an LCD display with the Arduino I’ve used the Arduino libraries (

#include LiquidCrystal.h) and then used:lcd.clear();

lcd.setCursor(0,0);

and when I wanted to clear only one line I couldn’t find a default method so I just did this:

void ClearLine(int line) {

String blankLine = ” “;

g_lcd.setCursor(0, line);

g_lcd.print(blankLine);

g_lcd.setCursor(0, line);

}

Hello, I’ve modified the code to allow the user to shift the phase of DDSB by 180 degrees in increments of 11.25 degrees. I would like to email it to you if you’re interested in using / posting it.

Thank you very much for the contribution – I can post it in your name or if you prefer an acount to post it yourself I can create that for you. I’m happy for you to send your version to: alex at tripsintech.com

Cheers,

Alex

Alex and all: Great article! A high-quality sine-wave quadrature oscillator for $30 or so… good tool for a ham shack.

Did Alan’s code get posted?

73’s Bob N3FM

Hi Bob,

Thanks for the feedback, all credit to John here I just offered an arduino version of the code!

Alan’s code: I have only just seen his email in which he did indeed send the code – thanks to your comment reminding me (I thought I had email forwarding setup but obviously not, so my bad) I shall get the code up shortly.

Cheers,

Alex

FYI – done

please send me ,DDSB by 180 degrees in increments of 11.25 degrees LCD latest Arduino code,Iam try it..best regards 73..

Hello Engin, Thank you for the contact. The code for the DDS in 11.25 deg steps is an altered, extended, version of the original Arduino C++ Quadrature code. which was crafted by Alex and myself. I do not have the code for the 11.2 degs step version. It may still be available on the TripsinTech page for that article. The code as found within my original article used only the 90 degs phase shift bit in the AD9850 phase shift control register, the other phase control bits allow for smaller steps and may be used in combination as needed. If you cannot find the other article then you will probably have little difficulty in making your own version of the code with smaller steps. You will find all the information needed in the AD9850 data sheet. Regards and 73 from John, G8GKU.

http://tripsintech.com/dual-ad9850-in-quadrature-and-finer-phase-adjustment/

Is the link to the other article with a link to the 11.25 degs code.

@John

many thanks and merry christmas.. 73

http://tripsintech.com/dual-ad9850-in-quadrature-and-finer-phase-adjustment/

Is the link to the other article with a link to the 11.25 degs code.

Happy Christmas!

Hello

I just recently found out about this article from you. I tried with your design, it works great if the frequency is less than 3MHz. In tests with frequencies greater than 10MHz, its phase and amplitude are no longer correct. While AD9850 can generate sine up to 40MHz

Can you help me explain?

Hello Anatoly, thank you for the interesting question regarding changes in amplitude and phase between the two initially quadrature outputs from the project, as operating frequency rises.

I believe you are seeing the effects of two dis-similar reconstruction filters. Each of the DDS PCB modules has a local filter which is placed between the AD9850 current output and the output pin at the edge of the PCB. Typically each filter has 2 resistors, 3 inductors and 7 capacitors. As the AD9850 output frequency rises, the effect of the two filters, built with ” standard tolerance ” parts, manifests as differences in amplitude and phase between the two filtered output signals. To ensure the * exact * same amplitude and phase response for each of the to filters would require extremely closely matched components in the two filters, in real terms, an unlikely situation.

I hinted at this behavior in my reply to Miguel Bartie dated 2016 – 02 – 18, you will find this in the complete comments list.

If quadrature relationship at higher frequencies, say, above 5 MHz, are needed in your project then I would suggest using just * one * AD9850 module and then to follow that with a hybrid quadrature power ” splitter “, chosen so that the operating frequency is at or near the centre of the pass band of the quadrature splitter.

An internet search will reveal the details of the most popular makes of commercial RF quadrature splitter.

I am hopeful this possible explanation has given you a guide to move your project forward.

Very best wishes, John G8GKU

Thank you for your reply and solution to this problem.

Best wishes! Anatoly